### UFO Ultra fast X-ray imaging of scientific processes with on-line assessment and data-driven process control

### Outline

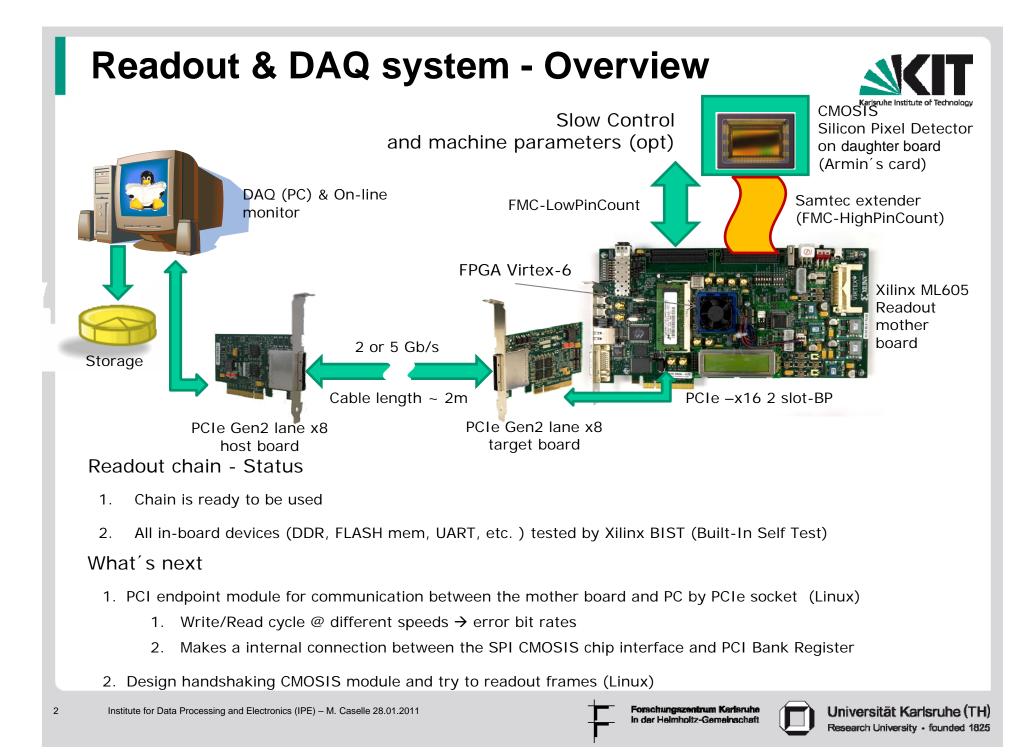

• Readout electronic & DAQ (Data AcQuisition) system → overview and status

Forschungszentrum Karlsruhe in der Helmholtz-Gemeinschaft

- CMOSIS silicon pixel detector  $\rightarrow$  some considerations

- Strategy to improve both 'fast reject algorithm' and 'CMOSIS readout time'

Universität Karlsruhe (TH)

Research University . founded 1825

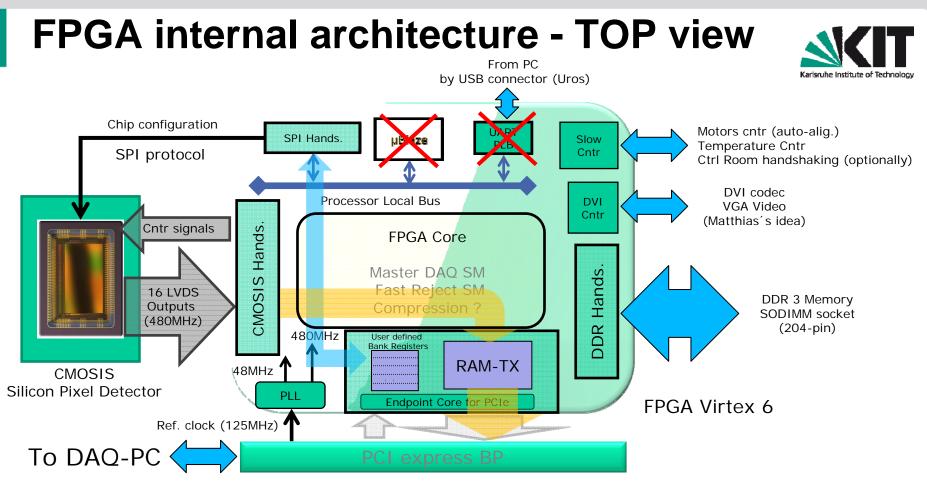

### Fpga firmware - Status

3

1. SPI Handshaking,  $\mu$ Blaze processor and UART interphase modules  $\rightarrow$  generated by Uros

2. PCI top module (included Bank Register and RAM)  $\rightarrow$  development actually under way (Matthias and Michele) What's next

- 1. Connection between Bank Register and SPI Handshaking  $\rightarrow$  to configure the CMOSIS directly by PCIe

- 2. CMOSIS Handshaking module and internal sequencer for free running frame acquisition (Michele)

- 3. DDR Handshaking and memory Cntr + Fast Reject algorithm modules (Michele and volunteer....)

Universität Karlsruhe (TH) Research University • founded 1825

## **CMV2000 Silicon Pixel Detector**

Sensitive area consists in 2048x1088 pixels (5.5x5.5  $\mu$ m<sup>2</sup>), 5 $\mu$ m thick epi-layer Column ADC converts the analog pixel value (energy released)  $\rightarrow$  10-12 bits Reset noise (KT/C) cancelling through the Correlated Double Sampling Fixed pattern noise is < 1LSB in 10 bit mode  $\rightarrow$  with a SNR =60dB

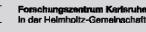

### CMOSIS and FPGA handshaking for data taking

Internal exposure  $\rightarrow$  the exposure time is set by programming the appropriate register by SPI interface.

External exposure → exposure time is defined externally by T\_EXP1 & Frame\_REQ input pins

The `CMOSIS Interface module (FPGA)' will generate both control signals and Frame\_REQ & T\_EXP1 for a flexible control of the exposure time.

**N.B** When the Readout chain will be available  $\rightarrow$  As soon as the CMOSIS chip characterization could start  $\rightarrow$  Offset (pixel threshold), gain, exposure time, Piecewise linear response, etc (Tomy's suggestion)

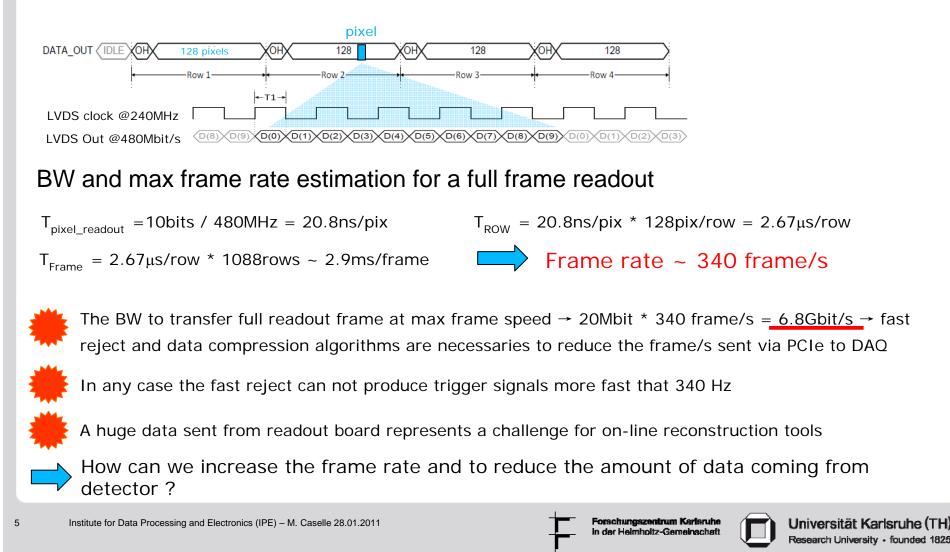

## **CMOSIS readout timing estimation**

Column-wise organized Readout by 16 LVDS output channels, each LVDS reads out 128 adjacent columns @ 480 Mbit/s

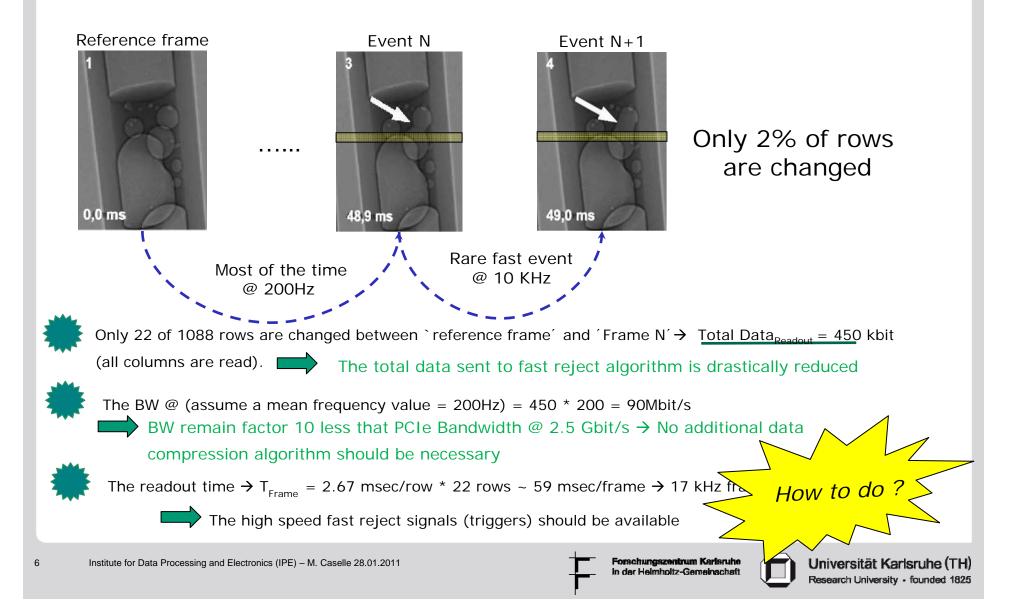

## Subsampling interesting region strategy

BW estimation in a real case  $\rightarrow$  both the temporal and spatial redundancies are considered

# Sub-sampling strategy for rows 'fast reject'

To maintain the same field of view but reduce the amount of data coming out of the detector, a subsampling mode is implemented on the chip  $\rightarrow$  could be used to split a full frame in several distinct frames

Full frame is split in two different frames:

$Frame_1 \rightarrow contain only the odd lines (white rows)$  $Frame_2 \rightarrow contain only the even lines (red rows)$

$T_{Frame} = 2.67 \ \mu sec/row * 544 \ rows \sim 1.45 \ msec/frame \rightarrow about 700 \ frame/sec$

### For more frames

7

$T_{Frame} = 2.67 \ \mu sec/row * 109 \ rows \sim 291 \ \mu sec/frame \rightarrow about 3.4 K \ frame/sec$  for 10 frames

$T_{Frame}$  = 2.67 µsec/row \* 54 rows ~ 145µsec/frame → about 7K frame/sec for 20 frames

The subsampling allows to design 'fast reject' algorithm operating @ kHz range and with a considerable reduction of data coming from the detector

#### Sub-sampling strategy for rows 'fast reject' Allows to generate fast reject signals (triggers) @ rows level $\rightarrow$ starting from a reference image<sup>Karisruhe Institute of Technolog</sup> Subsampling strategy is used to allow a fast readout frame @ kHz range Fast Data synchronization EXOR-elaboration Counter-elaboration Pipeline Output Fetch row Reference image (N+1)(row N) (row N-1) (row N-2) (row N-3) Pipeline Number of Rows Event trigger comparison Beam pixel changed fluctuation detection Veto Reg Row trigger counter leg Signals 0.0 ms eg ĝ Row Reg threshold Pixel threshold, **DAQ State** 48,9 ms Machine Next events User defined by in software FPGA core **Event Readout** To limit the amount of data and increase the frame rate from sensor, windowing in Y direction is possible. The number of lines and start address can be set by SPI Readout of a window around the row trigger signal. ∕∖∖ or full frame can be requested SPI chip configuration Optionally the multiple windows can be defined when a signals 48.9 ms multiple rows trigger are presents

8

Forschungszentrum Karlsruhe in der Helmholtz-Gemeinschaft

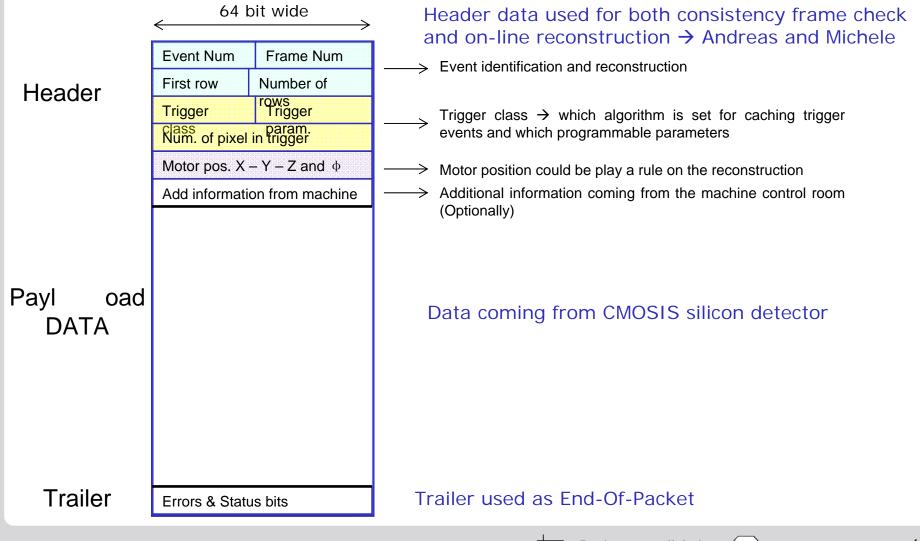

## Preliminary data format proposal

The data stream coming from detector will be re-formatted before to be sent to on-line PC.

Forschungszentrum Karlsruhe In der Helmholtz-Gemeinschaft

Universität Karlsruhe (TH) Research University • founded 1825

## Conclusions & what's next

Conclusion

- The readout chain → tested and ready for data taking

- One 'Fast Reject` and `Readout' strategies have been defined → using both 'sub-sampling' and 'Windowing' built-in CMOSIS chip features

(Reference on CMOSIS datasheet pag. 26 – 29)

### What's next

- SPI chip configuration by PCIe  $\rightarrow$  must be developed

- ´CMOSIS readout module` → must be developed

- When the first readout chain is available, the CMOSIS chip characterization will start using a light source

Forschungszeninum Karlsruhe in der Heimholtz-Gemeinschaft

Universität Karlsruhe (TH) Research University • founded 1825